#### Unit-1

#### **BASIC COMPUTER ORGANIZATION AND DESIGN**

#### **1. Instruction Codes:**

- The organization of the computer is defined by its internal registers, the timing and control structure, and the set of instructions that it uses.

- *Program:* set of instructions that specify the operations, operands, and the sequence by which processing has to occur.

- *Instruction*: a binary code that specifies a sequence of micro-operations for the computer.

- **Instruction Code:** group of bits that instruct the computer to perform specific operation.

| Opcode | Address   |

|--------|-----------|

| Specce | 7 Iddiess |

- Instruction code is usually divided into two parts: Opcode and address(operand)

- *Operation Code (opcode)*:

- group of bits that define the operation

- Eg: add, subtract, multiply, shift, complement.

- No. of bits required for opcode depends on no. of operations available in computer.

- n bit opcode  $\geq 2^n$  (or less) operations

- o Address (operand):

- specifies the location of operands (registers or memory words)

- Memory words are specified by their address

- Registers are specified by their k-bit binary code

- k-bit address >= 2<sup>k</sup> registers

#### **Stored Program Organization:**

- The ability to store and execute instructions is the most important property of a general-purpose computer. That type of stored program concept is called stored program organization.

- The simplest way to organize a computer is to have one processor register and an instruction code format with two parts. The first part specifies the operation to be performed and the second specifies an address.

|         |                   | Memory<br>4096 × 16 |

|---------|-------------------|---------------------|

| 15 12 1 | 0                 | the second second   |

| Opcode  | Address           | Instructions        |

| In      | istruction format | (program)           |

|         |                   | A CONTRACTOR        |

| 5       | 0                 | Operands            |

| E       | Binary operand    |                     |

| E       | Binary operand    | (data)              |

| I       | Binary operand    |                     |

#### > The below figure shows the stored program organization

- > Instructions are stored in one section of memory and data in another.

- For a memory unit with 4096 words we need 12 bits to specify an address since  $2^{12} = 4096$ .

- If we store each instruction code in one 16-bit memory word, we have available four bits for the operation code (abbreviated opcode) to specify one out of 16 possible operations, and 12 bits to specify the address of an operand.

- > Accumulator (AC):

$\checkmark$  Computers that have a single-processor register usually assign to it the name accumulator and label it AC.

$\checkmark$  The operation is performed with the memory operand and the content of AC.

#### **Addressing of Operand:**

- Sometimes convenient to use the address bits of an instruction code not as an address but as the actual operand.

- When the second part of an instruction code specifies an operand, the instruction is said to have an*immediate operand*.

- When the second part specifies the address of an operand, the instruction is said to have a *direct address*.

- When second part of the instruction designate an address of a memory word in which the address of the operand is found such instruction have *indirect address*.

- One bit of the instruction code can be used to distinguish between a direct and an indirect address.

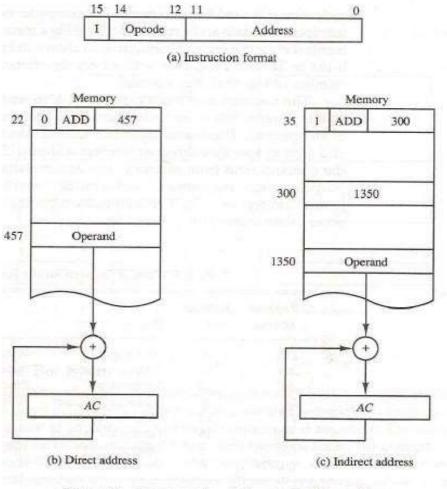

- The instruction code format shown in Fig. 5-2(a). It consists of a 3-bit operation code, a 12-bit address, and an indirect address mode bit designated by I. The mode bit is 0 for a direct address and 1 for an indirect address.

Figure 5-2 Demonstration of direct and indirect address.

- A direct address instruction is shown in Fig. 5-2(b).

- It is placed in address 22 in memory. The I bit is 0, so the instruction is recognized as a direct address instruction. The opcode specifies an ADD instruction, and the address part is the binary equivalent of 457.

- The control finds the operand in memory at address 457 and adds it to the content of AC.

- > The instruction in address 35 shown in Fig. 5-2(c) has a mode bit I = 1.

- > Therefore, it is recognized as an indirect address instruction.

- The address part is the binary equivalent of 300. The control goes to address 300 to find the address of the operand. The address of the operand in this case is 1350.

- > The operand found in address 1350 is then added to the content of AC.

- The *effective address* to be the address of the operand in a computation-type instruction or the target address in a branch-type instruction.

- Thus the effective address in the instruction of Fig. 5-2(b) is 457 and in the instruction of Fig 5-2(c) is 1350.

#### 2. Computer Registers:

- ✓ Need of Computer Registers

- Instruction sequencing needs a counter to calculate the address of the next instruction after execution of the current instruction is completed (**PC**).

- Necessary to provide a register in the control unit for storing the instruction code after it is read from memory (IR).

- Needs processor registers for manipulating data (AC and TR) and a register for holding a memory address (AR).

- ✓ The above requirements dictate the registers, their configuration, number of bits and their uses

| Register<br>symbol | Number<br>of bits | Register name        | Function                     |  |  |

|--------------------|-------------------|----------------------|------------------------------|--|--|

| DR                 | 16                | Data register        | Holds memory operand         |  |  |

| AR                 | 12                | Address register     | Holds address for memory     |  |  |

| AC                 | 16                | Accumulator          | Processor register           |  |  |

| IR                 | 16                | Instruction register | Holds instruction code       |  |  |

| PC                 | 12                | Program counter      | Holds address of instruction |  |  |

| TR                 | 16                | Temporary register   | Holds temporary data         |  |  |

| INPR               | 8                 | Input register       | Holds input character        |  |  |

| OUTR               | 8                 | Output register      | Holds output character       |  |  |

| - 10 C             | 11                | 0                    |                              |  |  |

|                    |                   | PC                   |                              |  |  |

|                    |                   |                      |                              |  |  |

|                    | 11                | 0                    |                              |  |  |

|                    |                   | AR                   |                              |  |  |

|                    | 13                | 24                   | Memory                       |  |  |

|                    |                   |                      | 4096 words                   |  |  |

| 15                 |                   | 0                    | 16 bits per word             |  |  |

|                    | IR                |                      |                              |  |  |

|                    |                   |                      |                              |  |  |

| 15                 |                   | 0                    | 15 0                         |  |  |

|                    | TR                |                      | DR                           |  |  |

| 7                  | 0 3               | 0                    | 15 0                         |  |  |

| 0                  | UTR               | INPR                 | AC                           |  |  |

- ✓ The *data register* (*DR*) holds the operand read from memory.

- $\checkmark$  The *accumulator* (*AC*) register is a general purpose processing register.

- $\checkmark$  The instruction read from memory is placed in the *instruction register* (*IR*).

- ✓ The *temporary register* (*TR*) is used for holding temporary data during the processing.

- ✓ The *memory address register* (AR) has 12 bits since this is the width of a memory address.

- ✓ The *program counter (PC)* also has 12 bits and it holds the address of the next instruction to be read from memory after the current instruction is executed.

- $\checkmark$  Two registers are used for input and output.

- The *input register (INPR)* receives an 8-bit character from an input device.

- The *output register (OUTR)* holds an 8-bit character for an output device.

#### **Common Bus System:**

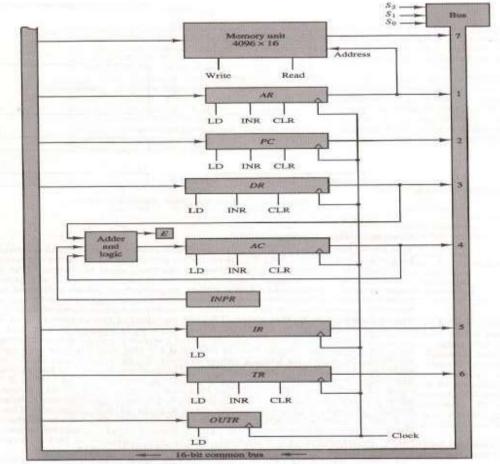

- $\checkmark$  The basic computer has eight registers, a memory unit, and a control unit

- ✓ Paths must be provided to transfer information from one register to another and between memory and registers.

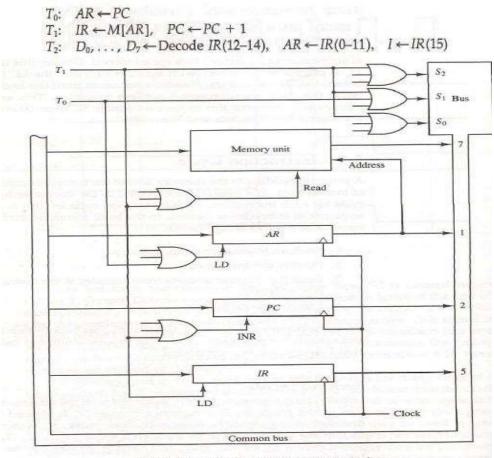

Figure 5-4 Basic computer registers connected to a common bus.

- A more efficient scheme for transferring information in a system with many registers is to use a common bus.

- > The connection of the registers and memory of the basic computer to a

common bus system is shown in Fig. 5-4.

- > The outputs of seven registers and memory are connected to the common bus.

- > The specific output that is selected for the bus lines at any given time is determined from the binary value of the selection variables  $S_2$ ,  $S_1$ , and  $S_0$ .

- The number along each output shows the decimal equivalent of the required binary selection.

> For example, the number along the output of *DR* is 3. The 16-bit outputs of DR are placed on the bus lines when  $S_2S_1S_0 = 011$ .

- The lines from the common bus are connected to the inputs of each register and the data inputs of the memory.

- The particular register whose LD (load) input is enabled receives the data from the bus during the next clock pulse transition.

- > The memory receives the contents of the bus when its write input is activated.

- > The memory places its 16-bit output onto the bus when the read input is activated and  $S_2S_1S_0 = 111$ .

- > Two registers, AR and PC, have 12 bits each since they hold a memory address.

- ➢ When the contents of AR or PC are applied to the 16-bit common bus, the four most significant bits are set to 0's.

- When AR or PC receives information from the bus, only the 12 least significant bits are transferred into the register.

- > The input register *INPR* and the output register OUTR have 8 bits each.

- > They communicate with the eight least significant bits in the bus.

- INPR is connected to provide information to the bus but OUTR can only receive information from the bus.

- > This is because INPR receives a character from an input device which is then transferred to AC.

- > *OUTR* receives a character from AC and delivers it to an output device.

- Five registers have three control inputs: LD (load), INR (increment), and CLR (clear).

- > This type of register is equivalent to a binary counter with parallel load and synchronous clear.

- > Two registers have only a LD input.

- The input data and output data of the memory are connected to the common bus, but the memory address is connected to AR.

- > Therefore, AR must always be used to specify a memory address.

- The 16 inputs of AC come from an adder and logic circuit. This circuit has three sets of inputs.

- One set of 16-bit inputs come from the outputs of AC.

- $\circ$  Another set of 16-bit inputs come from the data register *DR*.

- The result of an addition is transferred to *AC* and the end carry-out of the addition is transferred to flip-flop E (extended *AC* bit).

- A third set of 8-bit inputs come from the input register INPR.

- The content of any register can be applied onto the bus and an operation can be performed in the adder and logic circuit during the same clock cycle.

- > For example, the two microoperations  $DR \square AC$  and  $AC \square DR$  can be executed at the same time.

- > This can be done by placing the content of AC on the bus (with  $S_2S_1S_0 = 100$ ), enabling the LD (load) input of DR, transferring the content of DR through the adder and logic circuit into AC, and enabling the LD (load) input of AC, all during the same clock cycle.

#### **<u>3. Computer Instructions:</u>**

✓ The basic computer has three instruction code formats, as shown in Fig. 5-5. Each format has 16 bits.

| 15 | 14  |       | 12       | 11                      | 0 |                           |

|----|-----|-------|----------|-------------------------|---|---------------------------|

| I  | C   | pco   | de       | Address                 | 1 | (Opcode = 000 through 110 |

|    | (a) | ) Me  | mory     | - reference instruction |   |                           |

| 15 | 11  | 100   | 12       | 11                      | 0 |                           |

| 0  | 1   | 1     | 1        | Register operation      |   | (Opcode = 111, I = 0)     |

|    | (b  | ) Reg | gister · | - reference instruction |   |                           |

| 15 | -   | in    | 12       | 11                      | 0 |                           |

| 1  | 1   | 1     | 1        | I/0 operation           |   | (Opcode = 111, I = 1)     |

- ✓ The operation code (opcode) part of the instruction contains three bits and the meaning of the remaining 13 bits depends on the operation code encountered.

- ✓ A memory-reference instruction uses 12 bits(0-11) to specify an address, next 3 bits for operation code(opcode) and one bit to specify the addressing mode I. I is equal to 0 for direct address and to 1 for indirect address.

|       |        | Hexade | cimal code |                                 |

|-------|--------|--------|------------|---------------------------------|

| 1 = 0 | Symbol | 1=0    | 1 = 1      | Description                     |

| 0ххэ  | AND    | Онжн   | Вюся       | AND memory word to AC           |

| lao   | ADD    | 1 xxx  | 9жжж       | ADD memory word to AC           |

| 2:00  | LDA    | 2000   | Аххх       | LOAD Memory word to AC          |

| loo   | STA    | Jacos  | Васко      | Store content of AC i<br>memory |

| 4800  | BUN    | 4нжн   | Сяж        | Branch unconditionally          |

| 5100  | BSA    | 5xxxx  | Dxxx       | Branch and save return addres   |

| 6100  | isz    | 6хоос  | Еккх       | Increment and Skip if zero      |

✓ The register-reference instructions are recognized by the operation code 111 with a 0 in the leftmost bit (bit 15) of the instruction.

$\checkmark$  A register-reference instruction specifies an operation on the AC register. So an operand from memory is not needed. Therefore, the other 12(0-11) bits are used to specify the operation to be executed.

| Symbol | Hexadecimal code | Description                             |  |  |

|--------|------------------|-----------------------------------------|--|--|

| CLA    | 7800             | Clear AC                                |  |  |

| CLE    | 7400             | 0 Clear E                               |  |  |

| CMA    | 7200             | Complement AC                           |  |  |

| CME    | 7100             | Complement E                            |  |  |

| CIR    | 7080             | Circulate right AC and E                |  |  |

| CIL    | 7040             | Circulate left AC and E                 |  |  |

| INC    | 7020             | Increment AC                            |  |  |

| SPA    | 7010             | 10 Skip next instruction if AC positive |  |  |

| SNA    | 7008             | Skip next instruction is AC is negative |  |  |

| SZA    | 7004             | Skip next instruction is AC is 0        |  |  |

| SZE    | 7002             | Skip next instruction is E is 0         |  |  |

| HLT    | 7001             | Halt computer                           |  |  |

## **Register Reference Instructions**

- ✓ An **input—output instruction** does not need a reference to memory and is recognized by the operation code 111 with a 1 in the leftmost bit of the instruction.

- $\checkmark$  The remaining 12 bits are used to specify the type of input—output operation.

## I/O Reference Instructions

| Symbol | Hexadecimal code | Description                   |  |

|--------|------------------|-------------------------------|--|

| INP    | F800             | Input character to AC         |  |

| OUT    | F400             | F400 Output character from AC |  |

| SKI    | F200             | Skip on input flag            |  |

| SKO    | F100             | Skip on Output flag           |  |

| ION    | F080             | Interrupt on                  |  |

| IOF    | F040             | Interrupt off                 |  |

#### **Instruction Set Completeness:**

- ✓ A computer should have a set of instructions so that the user can construct machine language programs to evaluate any function.

- ✓ The set of instructions are said to be complete if the computer includes a sufficient number of instructions in each of the following categories:

- o Arithmetic, logical, and shift instructions

- Data Instructions (for moving information to and from memory and processor registers)

- Program control or Brach

- Input and output instructions

- ✓ There is one arithmetic instruction, ADD, and two related instructions, complement AC(CMA) and increment AC(INC). With these three instructions we can add and subtract binary numbers when negative numbers are in signed-2's complement representation.

- ✓ The circulate instructions, CIR and CIL; can be used for arithmetic shifts as well as any other type of shifts desired.

- ✓ There are three logic operations: AND, complement AC (CMA), and clear AC(CLA). The AND and complement provide a NAND operation.

- ✓ Moving information from memory to AC is accomplished with the load AC (LDA) instruction. Storing information from AC into memory is done with the store AC (STA) instruction.

- ✓ The branch instructions BUN, BSA, and ISZ, together with the four skip instructions, provide capabilities for program control and checking of status conditions.

- $\checkmark$  The input (INP} and output (OUT) instructions cause information to be transferred between the computer and external devices.

#### 4. <u>Timing and Control:</u>

- $\checkmark$  The timing for all registers in the basic computer is controlled by a master clock generator.

- ✓ The clock pulses are applied to all flip-flops and registers in the system, including the flip-flops and registers in the control unit.

- $\checkmark$  The clock pulses do not change the state of a register unless the register is enabled by a control signal.

- ✓ The control signals are generated in the control unit and provide control inputs for the multiplexers in the common bus, control inputs in processor registers, and microoperations for the accumulator.

- There are two major types of control organization: *Hardwired control and Microprogrammed control*

- ✓ The differences between hardwired and microprogrammed control are

| Hardwired control                                                                                      | Microprogrammed control                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ✓ The control logic is implemented with gates,<br>flip-flops, decoders, and other digital<br>circuits. | <ul> <li>The control information is stored in a<br/>control memory. The control memory is<br/>programmed to initiate the required<br/>sequence of microoperations.</li> </ul> |

| $\checkmark$ The advantage that it can be optimized to                                                 | $\checkmark$ Compared with the hardwired control                                                                                                                              |

| produce a fast mode of operation.                                                                      | operation is slow.                                                                                                                                                            |

| ✓ Requires changes in the wiring among the various components if the design has to be                  | <ul> <li>Required changes or modifications can be<br/>done by updating the microprogram in</li> </ul>                                                                         |

| modified or changed.                                                                                   | control memory.                                                                                                                                                               |

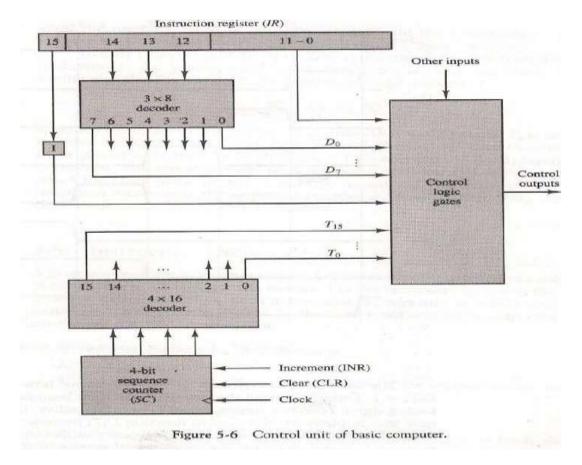

$\checkmark$  The block diagram of the hardwired control unit is shown in Fig. 5-6.

- $\checkmark$  It consists of two decoders, a sequence counter, and a number of control logic gates.

- ✓ An instruction read from memory is placed in the instruction register (IR). It is divided into three parts: The I bit, the operation code, and bits 0 through 11.

- ✓ The operation code in bits 12 through 14 are decoded with a 3 x 8 decoder. The eight outputs of the decoder are designated by the symbols D₀ through D<sub>7</sub>.

- $\checkmark$  Bit 15 of the instruction is transferred to a flip-flop designated by the symbol I.

- $\checkmark$  Bits 0 through 11 are applied to the control logic gates.

- $\checkmark$  The 4-bit sequence counter can count in binary from 0 through 15.

- $\checkmark$  The outputs of the counter are decoded into 16 timing signals T<sub>0</sub> through T<sub>15</sub>.

- $\checkmark$  The sequence counter *SC* can be incremented or cleared synchronously.

- ✓ The counter is incremented to provide the sequence of timing signals out of the 4 x 16 decoder.

- ✓ As an example, consider the case where *SC* is incremented to provide timing signals  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$  and  $T_4$  in sequence. At time  $T_4$ , *SC* is cleared to 0 if decoder output D3 is active.

- $\checkmark$  This is expressed symbolically by the statement

#### $D_3T_4$ : SC $\Box 0$

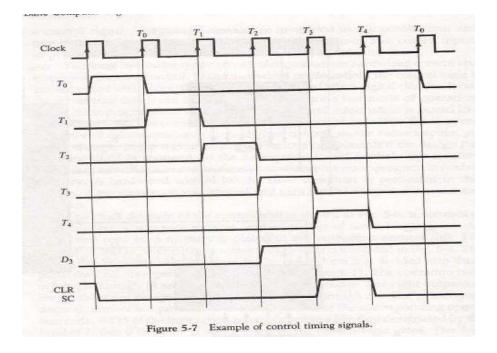

- $\checkmark$  The timing diagram of Fig. 5-7 shows the time relationship of the control signals.

- $\checkmark$  The sequence counter *SC* responds to the positive transition of the clock.

- ✓ Initially, the CLR input of SC is active. The first positive transition of the clock clears SC to 0, which in turn activates the timing signal T₀ out of the decoder. T₀ is active during one clock cycle.

- ✓ SC is incremented with every positive clock transition, unless its CLR input is active.

- ✓ This produces the sequence of timing signals  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$  and so on, as shown in the diagram.

- ✓ The last three waveforms in Fig.5-7 show how SC is cleared when  $D_3T_4 = 1$ .

- $\checkmark$  Output D<sub>3</sub> from the operation decoder becomes active at the end of timing signal T<sub>2</sub>.

- ✓ When timing signal  $T_4$  becomes active, the output of the AND gate that implements the control function  $D_3T_4$  becomes active.

- $\checkmark$  This signal is applied to the CLR input of *SC*. On the next positive clock transition (the one marked T4 in the diagram) the counter is cleared to 0.

- ✓ This causes the timing signal  $T_0$  to become active instead of  $T_5$  that would have been active if *SC* were incremented instead of cleared.

#### 5. Instruction Cycle:

- ✓ A program residing in the memory unit of the computer consists of a sequence of instructions.

- $\checkmark$  The program is executed in the computer by going through a cycle for each instruction.

- $\checkmark$  Each instruction cycle in turn is subdivided into a sequence of sub cycles or phases.

- $\checkmark$  In the basic computer each instruction cycle consists of the following phases:

- 1. Fetch an instruction from memory.

- 2. Decode the instruction.

- 3. Read the effective address from memory if the instruction has an indirect address.

- 4. Execute the instruction.

- ✓ Upon the completion of step 4, the control goes back to step 1 to fetch, decode, and execute the next instruction.

#### **Fetch and Decode:**

- ✓ Initially, the program counter PC is loaded with the address of the first instruction in the program.

- $\checkmark$  The sequence counter SC is cleared to 0, providing a decoded timing signal T<sub>0</sub>.

- ✓ The microoperations for the fetch and decode phases can be specified by the following register transfer statements.

Figure 5-8 Register transfers for the fetch phase.

- ✓ Figure 5-8 shows how the first two register transfer statements are implemented in the bus system.

- ✓ To provide the data path for the transfer of *PC* to AR we must apply timing signal  $T_0$  to achieve the following connection:

- Place the content of *PC* onto the bus by making the bus selection inputs  $S_2$ ,  $S_1$ ,  $S_0$  equal to 010.

- Transfer the content of the bus to AR by enabling the LD input of AR.

- ✓ In order to implement the second statement it is necessary to use timing signal  $T_1$  to provide the following connections in the bus system.

- Enable the read input of memory.

- Place the content of memory onto the bus by making  $S_2S_1S_0=111$ .

- Transfer the content of the bus to IR by enabling the LD input of IR.

- Increment PC by enabling the INR input of PC.

- ✓ Multiple input OR gates are included in the diagram because there are other control functions that will initiate similar operations.

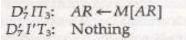

#### **Determine the Type of Instruction:**

• Initialise SC =0.

• Fetch phase

- At time T0 get the address of the next instruction to be executed from the Program Counter (PC).

$AR \leftarrow PC$

- At time T1 get the instruction from the memory address in AR into the Instruction Register (IR) and increment PC.

$IR \leftarrow M[AR]$  $PC \leftarrow PC + 1$

• Decode phase

- At time T2 decode the instruction by considering 12-14 bits of IR as Opcode, copy 0-11 bits of IR to AR and 15<sup>th</sup> bit to I flip flop.

- Decoding Phase at time T3 determines the type of instruction read from memory.

- Decoder output  $D_7$  is equal to 1 the instruction is a register reference or memory reference instruction.

- If I = 0 it is a register reference instruction.

- If I = 1 it is a I/O instruction. Execute the instruction and set SC =0.

• If D7 = 0 it is a memory reference instruction and the mode of address is determined from the I value.

- If I = 1, we have a memory reference instruction with an indirect address. The effective address is read from memory using the microoperation

$AR \leftarrow M[AR]$

- If D7=0 and I=0 Nothing is done. Execute the instruction and set SC=0.

After executing the instruction control shifts to process the next instruction.

$D_7 I'T_3$ : Execute a register-reference instruction

D7 IT3: Execute an input-output instruction

Figure 5-9 Flowchart for instruction cycle (initial configuration).

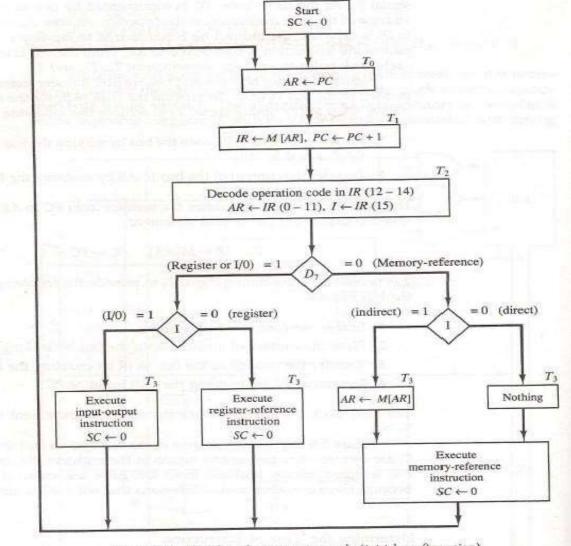

#### 6. Microprogrammed Control (Control Memory)

- **Microinstruction** : Each word in control memory contains within it a microinstruction.

- Microoperation : A microinstruction specifies one or more microoperations.

- **Microprogram** : A sequence of microinstructions forms what is called a microprogram.

- A computer that employs a microprogrammed control unit will have two separate memories:

1. The main memory : This memory is available to the user for storing programs. The user's program in main memory consists of machine instructions and data.

2. The control memory : This memory contains a fixed microprogram that cannot be alter by the user. The microprogram consists of microinstructions that specify various internal control signals for execution of register microoperations.

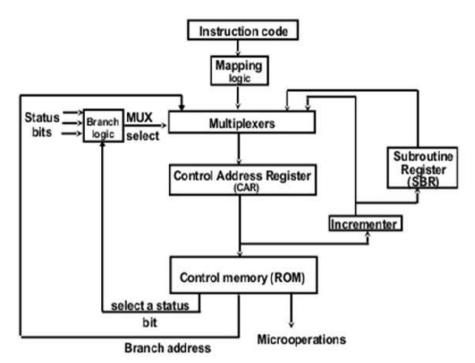

• Block diagram of microprogrammed control unit

Fig 3-1: Microprogrammed Control Organization

- Next Address Generator(Sequencer): It is used to generate the address of the next instruction to compute. The microinstruction contains bits to initiate the microoperations and bits to determine the address sequence for control memory. The next address can be determined as

- Loading an initial address to start the control operations.

- Incrementing the control address register

- Loading an address from control memory

- Transferring an external address.

- **Control Address Register** : It is used to hold the address of the instruction to be executed. It passes the address to the control memory.

- **Control Data Register**: It is holds the present microinstruction. It is also called Pipeline register. It allows the execution of the microoperations specified by the control word simultaneously with the generation of the next microinstruction.

- **Control Memory** : Control Memory is the storage in the microprogrammed control unit to store the microprogram. It is a ROM in which all control information is permanently stored.

- The microinstruction contains a control word that specifies one or more microoperations for the data processor. Once these operations are executed, the control must determine the next address.

• Advantage: Once the hardware configuration is established no need for further hardware or wiring changes. For different control sequence a different set of microinstructions is used in control memory.

#### **<u>7.</u>** Address Sequencing

- Microinstructions are usually stored in groups where each group specifies a routine, where each routine specifies how to carry out an instruction.

- Each routine must be able to branch to the next routine in the sequence.

- An initial address is loaded into the CAR when power is turned on; this is usually the address of the first microinstruction in the instruction fetch routine.

- Next, the control unit must determine the effective address of the instruction.

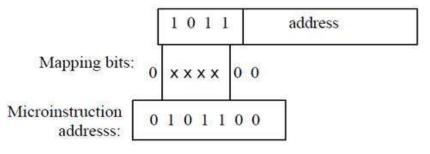

#### Mapping :

• The next step is to generate the microoperations that executed the instruction.

- This involves taking the instruction's opcode and transforming it into an address for the the instruction's microprogram in control memory. This process is called mapping.

- While microinstruction sequences are usually determined by incrementing the CAR, this is not always the case. If the processor's control unit can support subroutines in a microprogram, it will need an external register for storing return addresses.

- When instruction execution is finished, control must be return to the fetch routine. This is done using an unconditional branch.

- Addressing sequencing capabilities of control memory include:

- Incrementing the CAR

- Unconditional and conditional branching (depending on status bit).

- Mapping instruction bits into control memory addresses

- Handling subroutine calls and returns.

#### **Conditional Branching**

• Status bits

- provide parameter information such as the carry-out from the adder, sign of a number, mode bits of an instruction, etc.

– control the conditional branch decisions made by the branch logic together with the field in the microinstruction that specifies a branch address.

#### **Branch Logic**

- Branch Logic may be implemented in one of several ways:

- The simplest way is to test the specified condition and branch if the condition is true; else increment the address register.

- This is implemented using a multiplexer:

- If the status bit is one of eight status bits, it is indicated by a 3-bit select number.

- If the select status bit is 1, the output is 0; else it is 0.

- A 1 generates the control signal for the branch; a 0 generates the signal to increment the CAR.

- Unconditional branching occurs by fixing the status bit as always being 1.

#### **Mapping of Instruction**

- Branching to the first word of a microprogram is a special type of branch. The branch is indicated by the opcode of the instruction.

- The mapping scheme shown in the figure allows for four microinstruction as well as overflow space from 1000000 to 1111111.

Mapping of Instruction Code to Microoperation address

#### **Subroutines**

- Subroutine calls are a special type of branch where we return to one instruction below the calling instruction.

- Provision must be made to save the return address, since it cannot be written into ROM

## UNIT – II CENTRAL PROCESSING UNIT

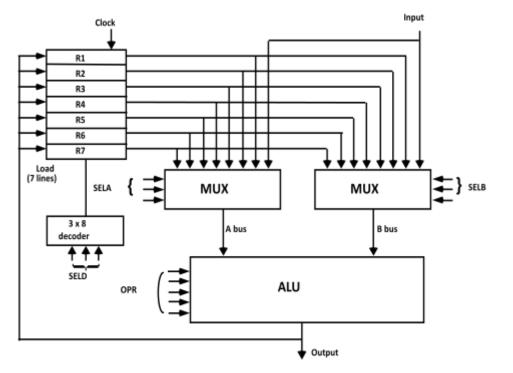

#### **1. GENERAL REGISTER ORGANIZATION**

- Generally CPU has seven general registers.

- Register organization show how registers are selected and how data flow between register and ALU.

- A decoder is used to select a particular register. The output of each register is connected to two multiplexers to form the two buses A and B.

- The selection lines in each multiplexer select the input data for the particular bus.

- The A and B buses form the two inputs of an ALU. The operation select lines decide the micro operation to be performed by ALU.

- The result of the micro operation is available at the output bus. The output bus connected to the inputs of all registers, thus by selecting a destination register it is possible to store the result in it.

#### **OPERATION OF CONTROL UNIT**

#### **Example: R1 <- R2 + R3**

- [1] MUX A selector (SELA): BUS A  $\leftarrow$  R2

- [2] MUX B selector (SELB): BUS  $B \leftarrow R3$

- [3] ALU operation selector (OPR): ALU to ADD

- [4] Decoder destination selector (SELD): R1  $\leftarrow$  Out Bus

|              | 3    | 3    | 3    | 5   |  |

|--------------|------|------|------|-----|--|

|              | SELA | SELB | SELD | OPR |  |

| Control Word |      |      |      |     |  |

Encoding of register selection fields

| Binary | SELA       | SELB       | SELD |

|--------|------------|------------|------|

| 000    | Input      | Input      | None |

| 001    | <b>R</b> 1 | <b>R</b> 1 | R1   |

| 010    | R2         | R2         | R2   |

| 011    | R3         | R3         | R3   |

| 100    | R4         | R4         | R4   |

| 101    | R5         | R5         | R5   |

| 110    | R6         | R6         | R6   |

| 111    | R7         | R7         | R7   |

### ALU CONTROL

Encoding of ALU Operations:

| OPR    |                |        |

|--------|----------------|--------|

| Select | Operation      | Symbol |

| 00000  | Transfer A     | TSFA   |

| 00001  | Increment A    | INCA   |

| 00010  | ADD A + B      | ADD    |

| 00101  | Subtract A - B | SUB    |

| 00110  | Decrement A    | DECA   |

| 01000  | AND A and B    | AND    |

| 01010  | OR A and B     | OR     |

| 01100  | XOR A and B    | XOR    |

| 01110  | Complement A   | COMA   |

| 10000  | Shift right A  | SHRA   |

| 11000  | Shift left A   | SHLA   |

#### Examples of ALU Microoperations

TABLE 3 Examples of Microoperations for the CPU

|                            |       | Symbolic | Designation |      |                   |  |

|----------------------------|-------|----------|-------------|------|-------------------|--|

| Microoperation             | SELA  | SELB     | SELD        | OPR  | Control Word      |  |

| R1 ← R2 - R3               | R2    | R3       | R1          | SUB  | 010 011 001 00101 |  |

| $R4 \leftarrow R4 \lor R5$ | R4    | R5       | R4          | OR   | 100 101 100 01010 |  |

| $R6 \leftarrow R6 + 1$     | R6    | _        | R6          | INCA | 110 000 110 00001 |  |

| R7 ← R1                    | R1    | _        | R7          | TSFA | 001 000 111 00000 |  |

| Output ← R2                | R2    | N        | None        | TSFA | 010 000 000 00000 |  |

| Output ← Input             | Input | _        | None        | TSFA | 000 000 000 00000 |  |

| R4 ← sh1 R4                | R4    |          | R4          | SHLA | 100 000 100 11000 |  |

| R5 ← 0                     | R5    | R5       | R5          | XOR  | 101 101 101 01100 |  |

#### 2. STACK ORGANIZATION

- The two operations that are performed on stack are the insertion and deletion.

- The operation of insertion is called **PUSH.**

- The operation of deletion is called **POP**.

- These operations are simulated by incrementing and decrementing the stack pointer register (SP).

#### Adv:

- Efficient computation of complex arithmetic expressions.

- Execution of instructions is fast because operand data are stored in consecutive memory locations.

- Length of instruction is short as they do not have address field.

#### **Disadv:**

• The size of the program increases.

#### **REGISTER STACK ORGANIZATION**

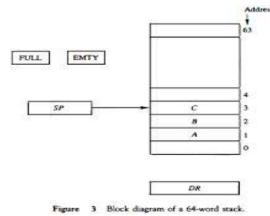

- A stack can be placed in a portion of a large memory or it can be organized as a collection of a finite number of memory words or registers.

- The figure shows the organization of a 64-word register stack

The stack pointer register SP contains a binary number whose value is equal to the address of the word is currently on top of the stack.

- Three items are placed in the stack: A, B, C, in that order.

- In above figure C is on top of the stack so that the content of SP is 3.

- For removing the top item, the stack is popped by reading the memory word at address 3 and decrementing the content of stack SP.

- Now the top of the stack is B, so that the content of SP is 2.

- Similarly for inserting the new item, the stack is pushed by incrementing SP and writing a word in the nexthigher location in the stack.

- In a 64-word stack, the stack pointer contains 6 bits because  $2^6 = 64$ .

- Since SP has only six bits, it cannot exceed a number greater than 63 (111111 in binary).

- When 63 is incremented by 1, the result is 0 since 111111 + 1 = 1000000 in binary, but SP can accommodate only the six least significant bits.

- Then the one-bit register FULL is set to 1, when the stack is full.

- Similarly when 000000 is decremented by 1, the result is 111111, and then the onebit register EMTY is set 1 when the stack is empty of items.

- DR is the data register that holds the binary data to be written into or read out of the stack.

#### **PUSH:**

- Initially, SP is cleared to 0, EMTY is set to 1, and FULL is cleared to 0, so that SP points to the word at address 0 and the stack is marked empty and not full.

- If the stack is not full (if FULL = 0), a new item is inserted with a push operation.

- The push operation is implemented with the following sequence of microoperations:

$SP \leftarrow SP + 1$   $M[SP] \leftarrow DR$  IF(SP = 0)then (FULL  $\leftarrow 1$ )  $EMTY \leftarrow 0$

- The stack pointer is incremented so that it points to the address of next-higher word.

- A memory write operation inserts the word from DR the top of the stack.

- The first item stored in the stack is at address 1. The last item is stored at address 0.

- If SP reaches 0, the stack is full of items, so FULL is to 1. This condition is reached if the top item prior to the last push way location 63 and, after incrementing SP, the last item is stored in location 0.

- Once an item is stored in location 0, there are no more empty registers in the stack, so the EMTY is cleared to 0.

POP:

- A new item is deleted from the stack if the stack is not empty (if EMTY = 0).

- The pop operation consists of the following sequence of min operations:

$DR \leftarrow M[SP]$   $SP \leftarrow SP + 1$   $IF(SP = 0) then (EMTY \leftarrow 1)$  $FULL \leftarrow 0$

- The top item is read from the stack into DR.

- The stack pointer is then decremented. If its value reaches zero, the stack is empty, so EMTY is set 1. This condition is reached if the item read was in location 1. Once this it is read out, SP is decremented and reaches the value 0, which is the initial value of SP.

- If a pop operation reads the item from location 0 and then is decremented, SP changes to 111111, which is equivalent to decimal 63 in above configuration, the word in address 0 receives the last item in the stack.

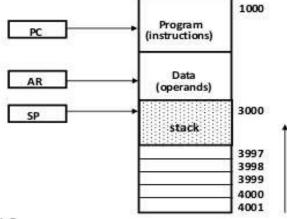

#### MEMORY STACK ORGANIZATION

1a

- A portion of memory is used as a stack with a processor register as a stack pointer

- The program counter PC points at the address of the next instruction in program. PC is used during the fetch phase to read an instruction.

- The address register AR points at an array of data. AR is used during the exec phase to read an operand.

- The stack pointer SP points at the top of the stack. SP is used to push or pop items into or from stack.

- The three registers are connected to a common address bus, and either one can provide an address for memory.

- As shown in Fig., the initial value of SP is 4001 and the stack grows with decreasing addresses. Thus the first item stored in the stack is at address 4000, the second item is stored at address 3999, and the last address that can be used for the stack is 3000. No provisions are available for stack limit checks.

- A new item is inserted by the PUSH operation. The stack pointer is decremented so that it points at the address of the next word. A memory write operation inserts the word from DR into the top of stack.

$SP \leftarrow SP - 1$  $M[SP] \leftarrow DR$

• An element is deleted from the stack using POP operation. The top item is read from the stack into DR. The stack pointer is then decremented to point at the next item in the stack.

$DR \leftarrow M[SP]$  $SP \leftarrow SP + 1$

• Most computers do not provide hardware to check stack overflow (full stack) or underflow(empty stack).

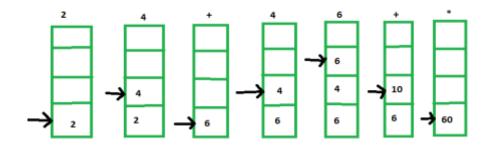

#### **Reverse Polish Notation:**

A stack organization is very effective for evaluating arithmetic expressions.

The common arithmetic expressions are written in infix notation, with each operator written between the operands. An expression can also be expressed in Prefix or Postfix notation as follows:

Eg: A+B -----> Infix notation +AB ----> Prefix or Polish notation AB+ ----> Post or reverse Polish notation

#### **Evaluation of Arithmetic Expressions:**

- Convert the expression from infix to postfix form.

- Scan the expression from left to right.

- When an operand is found PUSH it into the stack.

- When an operator is encountered POP two operands from the stack and perform the operation and PUSH the result into the stack.

- When the expression is scanned completely the final result is found in the TOP of the Stack.

- Consider the arithmetic expression

• In reverse polish notation, it is expressed as

Stack operations to evaluate (2+4)\*(4+6)

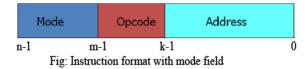

#### **3. Instruction Formats:**

- The bits of the instruction are divided into groups called fields.

- The most common fields found in instruction formats are:

- An operation code field that specifies the operation to be perform

- An address field that designates a memory address or a processor register.

- A mode field that specifies the way the operand or the effective address is determined.

- Computers may have instructions of several different lengths containing varying number of addresses.

- The number of address fields in the instruct format of a computer depends on the internal organization of its registers.

- Most computers fall into one of three types of CPU organizations:

- 1. Single accumulator organization.

- 2. General register organization.

- 3. Stack organization.

#### Single Accumulator Organization:

- In an accumulator type organization all the operations are performed with an implied accumulator register.

- The instruction format in this type of computer uses one address field.

- For example, the instruction that specifies an arithmetic addition defined by an assembly language instruction as

#### ADD $X \leftarrow AC$

where X is the address of the operand. The ADD instruction in this case results in the operation AC +M[X]. AC is the accumulator register and M[X] symbolizes the memory word located at address X.

- General register organization:

- The instruction format in this type of computer needs three register address fields.

- Thus the instruction for an arithmetic addition may be written in an assembly language as

#### ADD R1, R2, R3

to denote the operation  $R1 \leftarrow R2 + R3$ . The number of address fields in the instruction can be reduced from three to two if the destination register is the same as one of the source registers. Only register addresses for R1 and R2 need be specified in this instruction.

#### **Stack organization:**

- The stack-organized CPU has PUSH and POP instructions which require an address field.

- Thus the instruction PUSH X will push the word at address X to the top of the stack.

- The stack pointer is updated automatically.

- Stack type instructions do not need an address field in stack-organized computers since all operands are implied to be in the top of the stack.

Most computers fall into one of the three types of organizations. Some computers combine features from more than one organizational structure.

- On the basis of number of address, instruction are classified as:

- Three Address Instructions

- Two Address Instructions

- One Address Instructions

- Zero Address Instructions

#### **Three Address Instruction**

- This has three address field to specify a register or a memory location.

- Program created are much short in size but number of bits per instruction increase.

- Makes Program creation easier.

- Programs run much slow because instruction contains too many bits of information

- Expression: X = (A+B)\*(C+D)

- R1, R2 are registers. M[] is any memory location

- It can be implemented using three address instruction as

| ADD | R1, A, B  | $//\mathbf{R1} = \mathbf{M}[\mathbf{A}] + \mathbf{M}[\mathbf{B}]$ |

|-----|-----------|-------------------------------------------------------------------|

| ADD | R2, C, D  | //R2 = M[C] + M[D]                                                |

| MUL | X, R1, R2 | //M[X] = R1 * R2                                                  |

#### **Two Address Instruction**

- This is common in commercial computers. Here two address can be specified in the instruction.

- Expression:  $X = (A+B)^*(C+D)$

- R1, R2 are registers . M[] is any memory location.

- Program using two address instruction

| MOV | R1, A        | //R1 = M[A]                           |

|-----|--------------|---------------------------------------|

| ADD | R1, B        | //R1 = R1 + M[B]                      |

| MOV | <b>R2, C</b> | //R2 = C                              |

| ADD | R2, D        | //R2 = R2 + D                         |

| MUL | R1, R2       | //R1 = R1 * R2                        |

| MOV | X, R1        | // <b>M</b> [ <b>X</b> ] = <b>R</b> 1 |

#### **One address instruction**

- This use a implied ACCUMULATOR register for data manipulation.

- One operand is in accumulator and other is in register or memory location.

- Implied means that the CPU already know that one operand is in accumulator so there is no need to specify it.

- Expression: X = (A+B)\*(C+D)

- AC is accumulator. M[] is any memory location M[T] is temporary location.

- Program using one address instruction

| LOAD  | Α | $//\mathbf{AC} = \mathbf{M}[\mathbf{A}]$          |

|-------|---|---------------------------------------------------|

| ADD   | B | $//\mathbf{AC} = \mathbf{AC} + \mathbf{M[B]}$     |

| STORE | Т | $//\mathbf{M}[\mathbf{T}] = \mathbf{A}\mathbf{C}$ |

| LOAD  | С | $//\mathbf{AC} = \mathbf{M}[\mathbf{C}]$          |

| ADD   | D | //AC = AC + M[D]                                  |

| MUL   | Т | //AC = AC * M[T]                                  |

| STORE | Χ | $//\mathbf{M}[\mathbf{X}] = \mathbf{A}\mathbf{C}$ |

#### Zero address instruction

- A stack based computer do not use address field in instruction. To evaluate a expression first it is converted to revere Polish Notation i.e. Post fix Notation.

- Expression:  $X = (A+B)^*(C+D)$

- Postfixed : X = AB + CD + \*

- TOP means top of stack. M[X] is any memory location

- Program using zero address instruction

| DUCII |   |                                           |

|-------|---|-------------------------------------------|

| PUSH  | Α | //TOP = A                                 |

| PUSH  | B | //TOP = B                                 |

| ADD   |   | //TOP = A+B                               |

| PUSH  | С | //TOP = C                                 |

| PUSH  | D | //TOP = D                                 |

| ADD   |   | //TOP = C+D                               |

| MUL   |   | //TOP = (C+D)*(A+B)                       |

| POP   | Χ | $//\mathbf{M}[\mathbf{X}] = \mathbf{TOP}$ |

|       |   |                                           |

#### 4. ADDRESSING MODES

- Addressing modes refers to the way in which the operand of an instruction is specified.

- The addressing mode specifies a rule for interpreting or modifying the address field of the instruction before the operand is actually executed.

- The purpose of using addressing modes is as follows:

- To give the programming versatility to the user.

- To reduce the number of bits in addressing field of instruction.

#### **Types Of Addressing Mode**

- Implied Mode

- Immediate Mode

- Register Mode

- Register Indirect Mode

- Auto-Increment or Auto-Decrement Mode

- Direct Mode

- Indirect Mode

- Relative Addressing Mode

- Indexed Addressing mode

- Base Register Addressing Mode

#### **Implied Mode**

In this addressing mode, the instruction itself specifies the operands implicitly. It is also called as implicit addressing mode. All register-reference instructions that make use of the Accumulator are Implied Mode instructions.

Examples:

- The instruction "Complement Accumulator" is an implied mode instruction.

- RAL Rotate Left with Carry

#### **Immediate Mode**

In this addressing mode, the operand is specified in the instruction explicitly. Instead of address field, an operand field is present that contains the operand.

- Examples:

- ADD 10 will increment the value stored in the accumulator by 10.

- MOV R,20 initializes register R to a constant value 20.

#### **Register Mode**

In this mode the operand is stored in the register and this register is present in CPU. The instruction has the address of the Register where the operand is stored.

Advantages

- Shorter instructions and faster instruction fetch.

- Faster memory access to the operand(s)

Disadvantages

- Very limited address space

- Using multiple registers helps performance but it complicates the instructions.

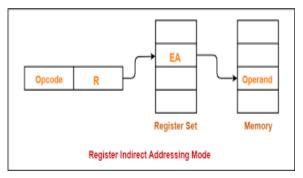

#### **Register Indirect Mode**

• In this mode, the instruction specifies the register whose contents give us the address of operand which is in memory. Thus, the register contains the address of operand rather than the operand itself.

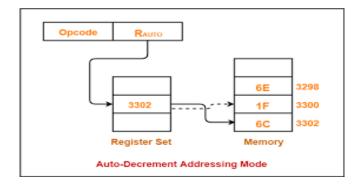

#### Auto increment or auto decrement mode

Effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of the register are automatically incremented or automatically decremented to the next consecutive memory location. Example: Add R1, (R2)+, Add R1, -(R2)

#### **Effective Address**

- The memory address of an operand consists of two components:

- Starting address of memory segment.

- Effective address or Offset: An offset is determined by adding any combination of three address elements: displacement, base and index.

- Displacement: It is an 8 bit or 16 bit immediate value given in the instruction.

- Base: Contents of base register, BX or BP.

- Index: Content of index register SI or DI.

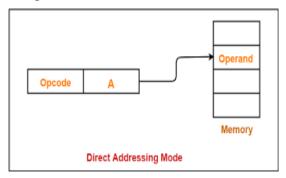

#### **Direct Addressing Mode**

• In this mode, effective address of operand is present in instruction itself. Single memory reference to access data.No additional calculations to find the effective address of the operand.

Example: ADD R1, 4000 - In this the 4000 is effective address of operand.

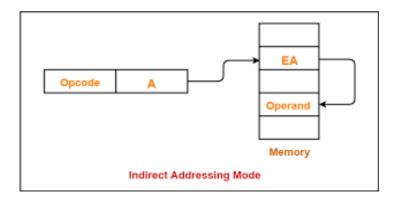

#### **Indirect Addressing Mode**

• In this, the address field of instruction gives the address where the effective address is stored in memory. This slows down the execution, as this includes multiple memory lookups to find the operand.

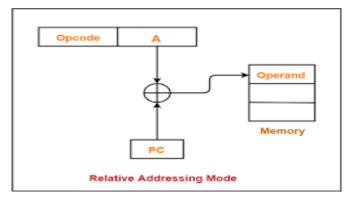

#### **Relative Addressing Mode**

In this the contents of PC(Program Counter) is added to address part of instruction to obtain the effective address.

EA = A + (PC), where EA is effective address and PC is program counter.

The operand is A cells away from the current cell(the one pointed to by PC)

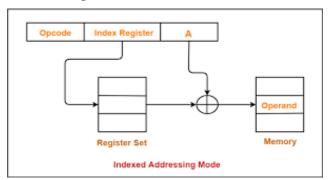

#### **Indexed Addressing Mode**

• In this the contents of the indexed register is added to the Address part of the instruction, to obtain the effective address of operand.

$\mathbf{E}\mathbf{A}=\mathbf{A}+(\mathbf{R}),$

In this the address field holds two values, A(which is the base value) and R(that holds the displacement), or vice versa.

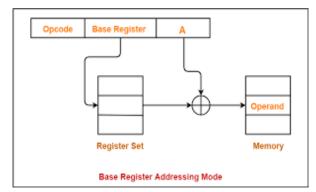

#### **Base Register Addressing Mode**

• It is again a version of Displacement addressing mode. This can be defined

as EA = A + (R), where A is displacement and R holds pointer to base address.

#### 5. DATA TRANSFER AND MANIPULATION

Most computer instructions can be classified into three categories

- Data transfer,

- Data manipulation,

- Program control instructions

#### **Data Transfer Instruction**

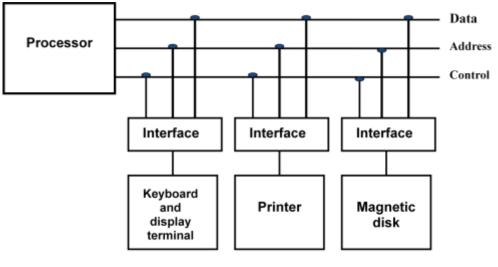

- Data transfer instructions move data from one place in the computer to another without changing the data content

- The most common transfers are between memory and processor registers, between processor registers and input or output, and between the processor registers themselves.

#### **Typical Data Transfer Instruction :**

| Name     | Mnemonic |

|----------|----------|

| Load     | LD       |

| Store    | ST       |

| Move     | MOV      |

| Exchange | XCH      |

| Input    | IN       |

| Output   | OUT      |

| Push     | PUSH     |

| Pop      | POP      |

Typical Data Transfer Instructions

- Load : transfer from memory to a processor register, usually an AC (memory read)

- **Store** : transfer from a processor register into memory (memory write)

- **Move** : transfer from one register to another register » Exchange : swap information between two registers or a register and a memory word

- Input/Output : transfer data among processor registers and input/output device

- Push/Pop : transfer data between processor registers and a memory stack

#### **Data Manipulation Instruction**

- Data Manipulation Instructions perform operations on data and provide the computational capabilities for the computer.

- It is divided into three basic types:

1) Arithmetic,

- 2) Logical and bit manipulation,

- 3) Shift Instruction

#### **Arithmetic Instructions**

**TABLE 8-7** Typical Arithmetic Instructions

| Name                    | Mnemonic |

|-------------------------|----------|

| Increment               | INC      |

| Decrement               | DEC      |

| Add                     | ADD      |

| Subtract                | SUB      |

| Multiply                | MUL      |

| Divide                  | DIV      |

| Add with carry          | ADDC     |

| Subtract with borrow    | SUBB     |

| Negate (2's complement) | NEG      |

#### Logical and bit manipulation Instructions

- Logical instructions performs binary operations on strings of bits stored in registers.

- They are useful for manipulating individual bits or group of bits that represent binary coded information.

| Name              | Mnemonic |

|-------------------|----------|

| CLEAR             | CLR      |

| COMPLEMENT        | COM      |

| AND               | AND      |

| OR                | OR       |

| EXCLUSIVE OR      | XOR      |

| CLEAR CARRY       | CLRC     |

| SET CARRY         | SETC     |

| COMPLEMENT CARRY  | COMC     |

| ENABLE INTERRUPT  | EI       |

| DISABLE INTERRUPT | DI       |

|                   |          |

#### **Shift Instructions**

• Shift are operations in which bits of a word are moved left or right.

#### Shift Instructions Name Mnemonic SHR Logical shift right Logical shift left SHL Arithmetic shift right SHRA Arithmetic shift left SHLA Rotate right ROR Rotate left ROL Rotate right through carry RORC Rotate left through carry ROLC

#### 6. PROGRAM CONTROL

• Program control instructions specify conditions for altering the content of the program counter , while data transfer and manipulation instructions specify condtions for data-processing operations.

| Name                     | Mnemonio |

|--------------------------|----------|

| Branch                   | BR       |

| Jump                     | JMP      |

| Skip next instruction    | SKP      |

| Call procedure           | CALL     |

| Return from procedure    | RET      |

| Compare (by subtraction) | CMP      |

| Test (by ANDing)         | TEST     |

Typical Program Control Instructions

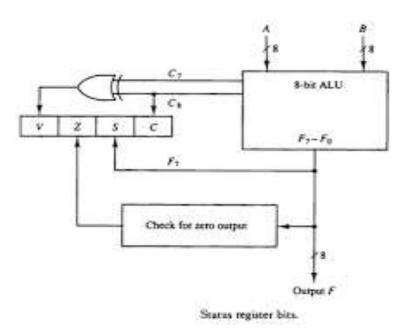

#### **Status Bit Conditions**

- It is convenient to supplement the ALU circuit in the CPU with a status register where status bit condition can be stored for further analysis.

- Status bits are also called condition code bit or flag bit.

- The four status bits are symbolized by C,S,Z and V.

- N bit is set if result of operation in negative (MSB = 1)

- Z bit is set if result of operation is zero (All bits = 0, AC=0)

- V bit is set if operation produced an overflow

- C bit is set if operation produced a carry (borrow on subtraction

- The bits are set or cleared as a result of an operation performed in the ALU.

# CONDITIONAL BRANCH INSTRUCTIONS

| Mnemonic | Branch condition      | Tested condition |

|----------|-----------------------|------------------|

| BZ       | Branch if zero        | Z = 1            |

| BNZ      | Branch if not zero    | $\mathbf{Z} = 0$ |

| BC       | Branch if carry       | C = 1            |

| BNC      | Branch if no carry    | C = 0            |

| BP       | Branch if plus        | S = 0            |

| BM       | Branch if minus       | S = 1            |

| BV       | Branch if overflow    | V = 1            |

| BNV      | Branch if no overflo  | $\mathbf{V} = 0$ |

| Unsig    | gned compare condit   | ions (A - B)     |

| BHI      | Branch if higher      | A > B            |

| BHE      | Branch if higher or   | equal A≥B        |

| BLO      | Branch if lower       | A < B            |

| BLOE     | Branch if lower or e  | qual A≤B         |

| BE       | Branch if equal       | A = B            |

| BNE      | Branch if not equal   | A ≠ B            |

| Signe    | d compare condition   | s (A - B)        |

| BGT      | Branch if greater th  | an A > B         |

| BGE      | Branch if greater or  |                  |

| BLT      | Branch if less than   | A < B            |

| BLE      | Branch if less or equ | ial A≤B          |

| BE       | Branch if equal       | A = B            |

| BNE      | Branch if not equal   | A ≠ B            |

22

#### **Subroutine Call and Return**

- It is a self-contained sequence of instructions that performs a given computational task.

- During the execution of a program, a subroutine may be called, when it is called, a branch is executed to the beginning of the subroutine to start executing its set of instructions.

- After the subroutine has been executed, a branch is made back to the main program.

- A subroutine call is implemented with the following microoperations: CALL:

| SP← SP-1                          | // Decrement stack point                                                             |

|-----------------------------------|--------------------------------------------------------------------------------------|

| M[SP] ←PC<br>PC←Effective Address | <pre>// Push content of PC onto the stack //Transfer control to the subroutine</pre> |

| RETURN:                           |                                                                                      |

| $PC \leftarrow M[SP]$             | // Pop stack and transfer to PC                                                      |

| $SP \leftarrow SP+1$              | // Increment stack pointer                                                           |

#### **Program Interrupt**

- Transfer program control from a currently running program to another service program as a result of an external or internal generated request.

- Control returns to the original program after the service program is executed

#### **Types of Interrupts**

#### 1) External Interrupts

Arises from I/O device, from a timing device, from a circuit monitoring the power supply, or from any other external source

#### 2) Internal Interrupts or TRAP

Caused by register overflow, attempt to divide by zero, an invalid operation code, stack overflow, and protection violation

#### 3) Software Interrupts

Initiated by executing an instruction (INT or RST) » used by the programmer to initiate an interrupt procedure at any desired point in the program

#### **Reduced Instruction Set Computer(RISC):**

A computer with large number instructions is classified as a complex instruction set computer, abbreviated as CISC.

The computer which having the fewer instructions is classified as a reduced instruction set computer, abbreviated as RISC.

#### **CISC Characteristics:**

- A large number of instructions--typically from 100 to 250 instructions.

- Some instructions that perform specialized tasks and are used infrequently.

- A large variety of addressing modes—typically from 5 to 20 differ modes.

- Variable-length instruction formats

- Instructions that manipulate operands in memory

#### **RISC Characteristics:**

- Relatively few instructions

- Relatively few addressing modes

- Memory access limited to load and store instructions

- All operations done within the registers of the CPU

- Fixed-length, easily decoded instruction format

- Single-cycle instruction execution

- Hardwired rather than microprogrammed control

- A relatively large number of registers in the processor unit

- Efficient instruction pipeline

## UNIT III COMPUTER ARITHMETIC

#### **Arithmetic Processor**

- Arithmetic instruction in digital computers manipulate data to produce results necessary for the solution of the computational problems.

- An arithmetic processor is the part of a processor unit that execute arithmetic instruction.

- An arithmetic instruction may specify binary or decimal data, and it may be represented in, Fixed point (integer or fraction) OR floating point form.

- An arithmetic processor is simple for binary fixed point add instruction

- Data types considered for the arithmetic operations are,

- Fixed-point binary data in signed magnitude representation

- Fixed-point binary data in signed-2's complement representation

- Floating point binary data

- o Binary -coded decimal (BCD) data

- Negative fixed point binary number can be represented in three ways,

- Signed magnitude (most computers use for floating point operations )

- Signed 1's complement

- Signed 2's complement(most computer use for integers)

#### 1. ADDITION AND SUBTRACTION WITH SIGNED-MAGNITUDE DATA

Eight different conditions to consider for addition and subtraction

|             | Add        | Subt         | ract Magnitudes |              |

|-------------|------------|--------------|-----------------|--------------|

| Operation   | Magnitudes | When $A > B$ | When $A < B$    | When $A = B$ |

| (+A) + (+B) | +(A + B)   |              |                 |              |

| (+A) + (-B) |            | +(A - B)     | -(B-A)          | +(A - B)     |

| (-A) + (+B) |            | -(A - B)     | +(B-A)          | +(A - B)     |

| (-A) + (-B) | -(A + B)   |              |                 |              |

| (+A) - (+B) |            | +(A - B)     | -(B-A)          | +(A - B)     |

| (+A) - (-B) | +(A + B)   |              |                 |              |

| (-A) - (+B) | -(A + B)   |              |                 |              |

| (-A) - (-B) |            | -(A - B)     | +(B - A)        | +(A - B)     |

#### Addition(Subtraction) algorithm

- When the signs of A and B are identical(different), add the two magnitudes and attach the sign of A to the result.

- When the sign of A and B are different(identical), compare the magnitudes and subtract the smaller number from the larger.

- Choose the sign of the result to be same as A if A > B or the complement of the sign of A if A < B.

- For equal magnitude subtract B from A and make the sign of the result

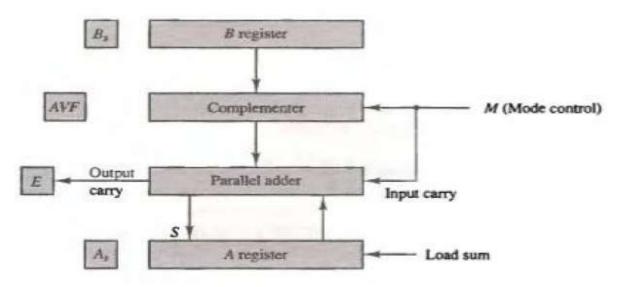

#### **Hardware Implementation**

- A and B be two registers that hold the magnitudes of No

- As and Bs be two flip-flops that hold the corresponding signs

- The Result is transferred into A and As.

- Parallel adder is needed to perform the micro operation A + B.

- Parallel subtractor are needed to perform A B or B A.

- Can be accomplished by means of complement and add

- Comparator circuit is needed to establish if A > B, A = B or A < B

- Comparison can be determine from the end carry after the subtraction

- The sign relationship can be determine from an exclusive-OR gate with As and Bs as inputs

- Output carry are transferred to E flip-flop

- Where it can be checked to determine the relative magnitude of the Nos.

- Add overflow flip-flop (AVF) holds the overflow bit when A and B are added.

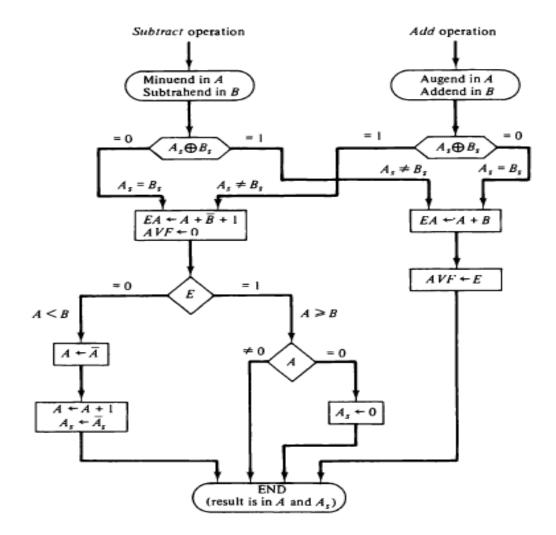

#### Hardware Algorithm

- The two signs A, and B, are compared by an exclusive-OR gate.

- If the output of the gate is 0 the signs are identical;

- If it is 1, the signs are different.

- For an add operation, identical signs dictate that the magnitudes be added. For a subtract operation, different signs indicate that the magnitudes be added.

- The magnitudes are added with a microoperation EA← A + B, where EA is a register that combines E and A.

- The carry in E after the addition constitutes an overflow if it is equal to 1. The value of E is transferred into the add-overflow flip-flop AVF.

- The two magnitudes are subtracted if the signs are different for an add operation or identical for a subtract operation.

- The magnitudes are subtracted by adding A to the 2's complemented B. No overflow can occur if the numbers are subtracted so AVF is cleared to 0.

- E=1 indicates that  $A \ge B$  and the number in A is the correct result. If this number is zero, the sign A must be made positive to avoid a negative zero.

- E=0 indicates that A < B. For this case it is necessary to take the 2's complement of the value in A. The operation can be done with one microoperation A ← A' +1.

- The sign of the result is the same as the sign of A. so no change in A is required. However, when A < B, the sign of the result is the complement of the original sign of A

- The final result is found in register A and its sign in As.

#### Addition and Subtraction with signed2's complement data

- The left most bit of binary number represents the sign bit; 0 for positive and 1 for negative.

- If the sign bit is 1, the entire the entire number is represented in 2's complement form.

- The addition of two numbers in signed-2's complement form consists of adding the number with the sign bits treated the same as the other bits of the number. A carry out of the sign bit position is discarded.

- The subtraction consists of first taking the 2's compliment of the subtrahend and then adding it to the minuend When two numbers of n digits each are added and the sum occupies n+1 Digits, we say that an overflow occurred.

- When the two carries are applied to an exclusive-OR gate, the overflow is detected when the output of the gate is equal to 1.

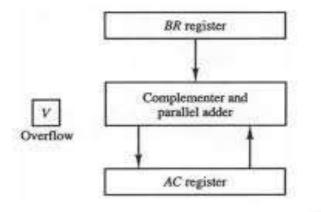

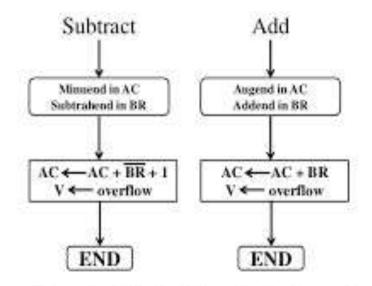

## Hardware for signed-2's Complement addition and subtraction

- The left most bit in AC and BR represents the sign bits of the numbers

- The over flow flip-flops V is set to 1 if there is an overflow. The output carry in this case is discarded.

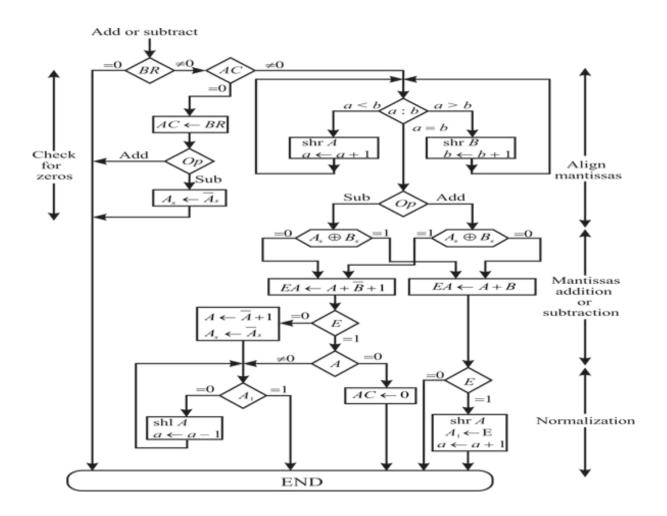

Figure: Algorithm for adding and subtracting numbers in signed-2's complement representation.

- The sum is obtained by adding the contents of AC and BR(including their sign bits).

- The overflow bit V is set to 1 if the ex-OR of the last two carries is 1,and it is cleared to 0 otherwise.

#### 2. Multiplication algorithms

Multiplication of two fixed point binary numbers in signed magnitude representation is done with paper and pencil of successive shift and add operation if the multiplier bit is a 1,the multiplicand is copied down; otherwise zero are copied down.

$\begin{array}{cccccccc} 23 & 10111 & Multiplicand \\ \underline{19} & \times 10011 & Multiplier \\ & 10111 & \\ & 10111 & \\ & 10111 & \\ & 00000 & + \\ & 00000 & \\ & 10111 & \\ 437 & 110110101 & Product \end{array}$

#### Hardware Implementation for Signed-Magnitude data

- Multiplication is conveniently implemented with two changes in the process

- -Use an adder to add binary numbers as there are bits in multiplier and successively accumulate the partial products in a register.

- Instead of shifting the multiplicand to the left , the partial product is shifted to the right

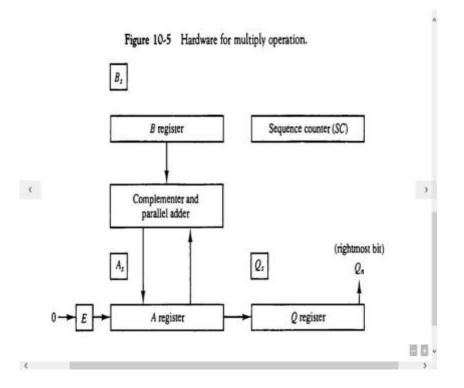

- The hardware for multiplication consists of registers Q, A and B.

- The multiplier stored in the Q register and its sign in Qs.

- The multiplicand is stored in B register and its sign in Bs.

- The sequence counter SC is initially set to a number equal to the number of bits in the multiplier. The counter is decremented by 1 after forming each partial product

- The sum of A and B forms a partial product which is transferred to the EA register.

- The shift will be denoted by the statement shr EAQ to designate the

- right shift depicted .

- The least significant bit of A is shifted into the most significant position of Q.

#### Hardware Algorithm

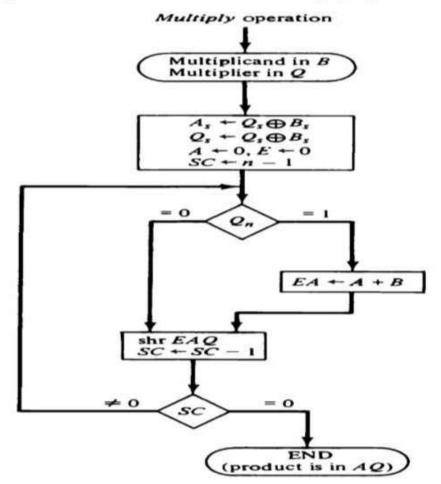

- Initially the multiplicand is in B and the multiplier in Q their corresponding signs are in Bs and Qs respectively.

- Register A and E are cleared and the sequence counter SC is set to a number equal to the number of bits of the multiplier.

- After the initialization , the low order bit of the multiplier in Qn is tested . If it is 1, the multiplicand In B is added to the present partial product in A . If it is 0, nothing is done .

- Register EAQ shifted once to the right to form the new partial product.

- The process stops when SC=0.

- Note that the partial product formed in A is shifted into Q one bit at a time and eventually replaces multiplier.

- The final product is available in both A and Q, with A holding the most significant bits and Q holding the least significant bits.

Figure 10-6 Flowchart for multiply operation.

TABLE 10-2 Numerical Example for Binary Multiplier

| Multiplicand $B = 10111$           | E             | Α     | Q     | SC  |

|------------------------------------|---------------|-------|-------|-----|

| Multiplier in Q                    | 0             | 00000 | 10011 | 101 |

| $Q_n = 1$ ; add B                  |               | 10111 |       |     |

| First partial product              | 0             | 10111 |       |     |

| Shift right EAQ                    | 0             | 01011 | 11001 | 100 |

| $Q_n = 1$ ; add B                  |               | 10111 |       |     |

| Second partial product             | 1             | 00010 |       |     |

| Shift right EAQ                    | 0             | 10001 | 01100 | 011 |

| $Q_n = 0$ ; shift right EAQ        | 0             | 01000 | 10110 | 010 |

| $Q_n = 0$ ; shift right EAQ        | 0             | 00100 | 01011 | 001 |

| $Q_n = 1$ ; add B                  |               | 10111 |       |     |

| Fifth partial product              | 0             | 11011 |       |     |

| Shift right EAQ                    | 0             | 01101 | 10101 | 000 |

| Final product in $AQ = 0110110101$ | E Contraction |       |       |     |

## 3. Booth's Multiplication Algorithm

- Booth algorithm gives a procedure for **multiplying binary integers** in **signed 2's complement representation in efficient way**, i.e., less number of additions/subtractions required.

- In this method the multiplier or multiplicand if it is negative number is represented in 2's complement representation.

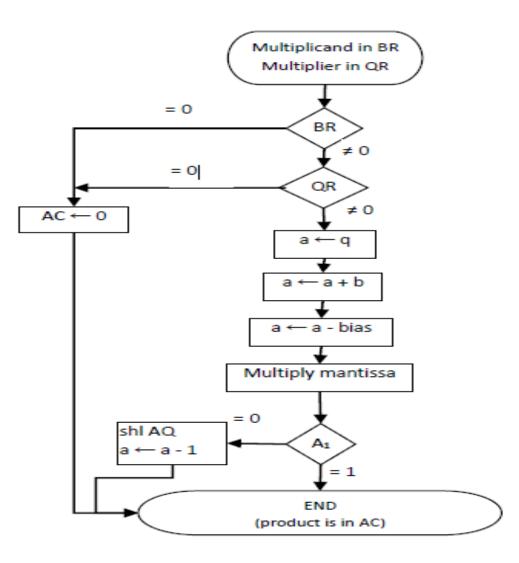

## Hardware Implementation of Booths Algorithm

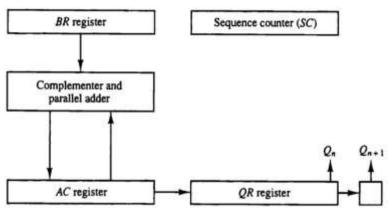

- The hardware implementation of the booth algorithm requires the register configuration shown in the figure below.

- The register used are AC, BR and QR respectively.

- $Q_n$  designates the least significant bit of multiplier in the register QR.

- An extra flip-flop  $Q_{n+1}$  is appended to QR to facilitate a double inspection of the multiplier

## Figure 10-7 Hardware for Booth algorithm.

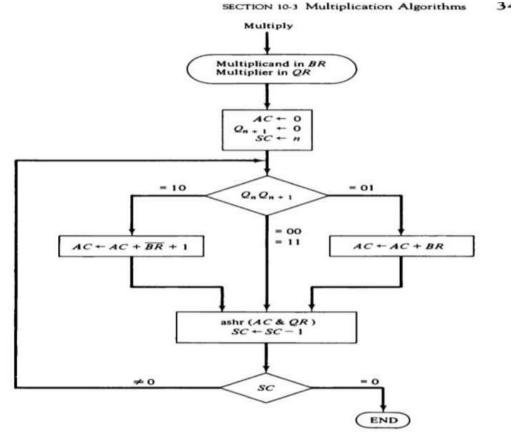

#### Algorithm

- Store the multiplicand in BR register and multiplier in QR register.

- Initialise AC and  $Q_{n+1}$  to zero. Initialise SC to the number of bits in the multiplier.

- The two bits of multiplier in  $Q_n$  and  $Q_{n+1}$  are inspected.

- If QnQn+1=10

- subtract BR from AC ie Add 2's complement of BR to AC .

- perform arithmetic right shift on AC & BR using ashr instruction.

- If QnQn+1=00 or 11 perform arithmetic right shift on AC & BR.

- If QnQn+1=01

- Add BR to AC

- perform arithmetic right shift on AC & BR.

- Decrement SC after each shift operation.

- Continue the steps until SC becomes zero.

- The product of the multiplication is present in AC and QR.

- Arithmetic right shift is shifts a bit to the right, it retains the sign(first) bit as such.

Figure 10-8 Booth algorithm for multiplication of signed-2's complement numbers.

Example

- Multiplying -9 and -13.

- Since both are negative numbers they are represented in 2's complement form.

- Binary of 9 = 01001

1's complement of 9 = 10110

2's complement of 9 = 10110 +1 = 10111 = -9

- Binary of 13 = 01101

1's complement of 13 =10010

2's complement of 13 = 10010+1 = 10011= -13

- The result is in AC & BR 0001110101 = 117

| 0.0 | 2++1 | $\frac{BR}{BR} = 10111$ $\frac{BR}{BR} + 1 = 01001$ | AC    | QR    | Q*+1 | SC  |

|-----|------|-----------------------------------------------------|-------|-------|------|-----|

|     |      | Initial                                             | 00000 | 10011 | 0    | 101 |

| 1   | 0    | Subtract BR                                         | 01001 |       |      |     |

|     |      |                                                     | 01001 |       |      |     |

|     |      | ashr                                                | 00100 | 11001 | 1    | 100 |

| 1   | 1    | ashr                                                | 00010 | 01100 | 1    | 011 |

| 0   | 1    | Add BR                                              | 10111 |       |      |     |

|     |      |                                                     | 11001 |       |      |     |

|     |      | ashr                                                | 11100 | 10110 | 0    | 010 |

| 0   | 0    | ashr                                                | 11110 | 01011 | 0    | 001 |

| 1   | 0    | Subtract BR                                         | 01001 |       |      |     |

|     |      |                                                     | 00111 |       |      |     |

|     |      | ashr                                                | 00011 | 10101 | 1    | 000 |

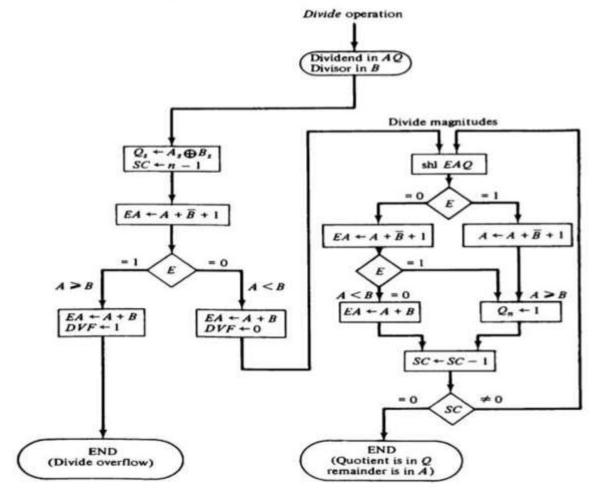

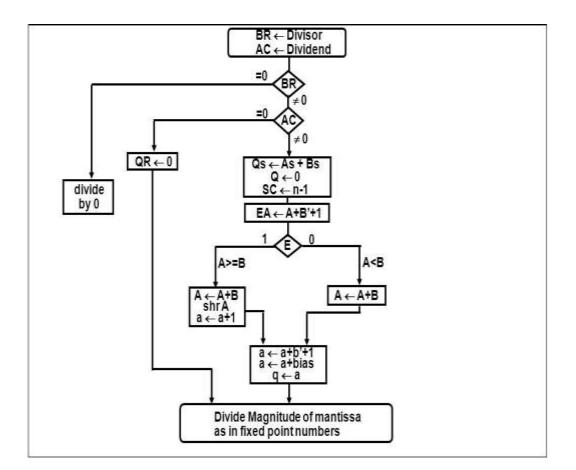

## 4. DIVISION ALGORITHMS

Division of two fixed-point binary numbers in signed magnitude representation is done with paper and pencil by a process of successive compare, shift, and subtract operations .

## **Binary Division**

| Divisor:         | 11010                                            | Quotient = $Q$                                                                                                             |